This document serves solely as a demonstration of AlphaClaim's technology and does not advocate legal or administrative action against any entity, including entities mentioned herein. This document neither alleges nor implies that any service or product from these entities infringes, either directly or indirectly, upon any patent or other intellectual property rights, including patents mentioned herein. This document neither alleges nor implies the invalidity or unenforceability of any patent, including patents mentioned herein.

This document was created independently by PriceWire, Inc. using AlphaClaim, for illustrative purposes only, without any third-party compensation or under any client contract or direction.

PriceWire, Inc. makes no representations or warranties regarding the completeness or accuracy of the information contained in this document and expressly disclaims any liability related to the use of such information for any purpose. PriceWire, Inc. is not a law firm, and this document does not provide legal advice.

### US20240061713A1 Case Study Report

This case study report reviews how AlphaClaim was used to automatically claim chart 923 references in 1 hour to find a high-quality invalidity ground (a well-motivated combination of two references) for claim 1 of US20240061713A1 (application 18/500,070). This ground could serve as part of an office action.

| Section                                      | Page # |

|----------------------------------------------|--------|

| What is AlphaClaim?                          | 3      |

| How does AlphaClaim work?                    | 4      |

| <b>Case &amp; Invalidity Ground Overview</b> | 5      |

| <b>Reviewed Grounds Scores</b>               | 6      |

| Generated Claim Chart                        | 7-10   |

#### What is AlphaClaim?

AlphaClaim is a "brain" that computes accurate and detailed claim charts for a variety of document types against a given set of claims, adhering to a preponderance of the evidence standard. AlphaClaim has been aligned on 1000s of PTAB IPR institution and final written decisions.

AlphaClaim performs automated, accurate, exhaustive claim charting of **superhuman quantities** of documents (often >10,000). For every document, AlphaClaim produces a claim chart with excerpts and explanations. It then computes an "AlphaScore" out of 5 for each claim element, indicating the strength of the document's disclosure of that element.

AlphaClaim can be applied in three ways. This document focuses on the first.

- (1) To **identify the best invalidity grounds** (including combinations), for IPRs or Office Actions. An AlphaScore of 4 or 5 indicates evidence stronger than the median IPR petition.

- (2) To identify evidence of patent validity prior to assertion or sale of a patent. If AlphaClaim's exhaustive review turns up low AlphaScores for all documents, a patent owner can be more confident that the patent will survive IPR or other 102/103 challenges.

- (3) To identify the best evidence of infringement, for patent owners.An AlphaScore of 4 or 5 indicates evidence stronger than the median filed claim chart.

| AlphaClaim | Claim<br>Element | Excerpt(s)                          | Alpha<br>Score | AlphaClaim's<br>Explanation                      |

|------------|------------------|-------------------------------------|----------------|--------------------------------------------------|

|            | A<br>method<br>  | "We<br>describe an<br>approach<br>" | 5.0            | The excerpt clearly<br>meets the<br>requirements |

#### How does AlphaClaim work?

AlphaClaim leverages many state-of-the-art AI technologies that are used in systems that achieve quality equivalent to the best humans, as detailed in the chart below. While computationally more expensive than consumer-grade chatbots, AlphaClaim achieves high quality with zero hallucination.

|                             | ChatGPT-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AlphaCode 2                         | AlphaGeometry                           | AlphaClaim                                            |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------|-------------------------------------------------------|

| Company                     | Image: Second secon | Google                              | Google                                  | AlphaClaim                                            |

| Purpose                     | Chatbot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Coding contests                     | Math Olympiad                           | Claim charting                                        |

| Quality Achieved            | Mixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Top 15% of ranked human competitors | Top ~60<br>mathematicians,<br>worldwide | Skilled IP attorney                                   |

| Specialization(s)           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fine-tuned,<br>sampling-based       | Custom pre-train,<br>symbolic engine    | Per-element score,<br>sampling, context<br>extraction |

| Hallucination Rate          | Substantial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Zero                                | Zero                                    | Zero                                                  |

| Computational<br>Complexity | 1x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | >1,000x                             | >1,000x                                 | >1,000x                                               |

AlphaClaim has 8 patents pending for its technological innovations.

#### Case & Invalidity Ground Overview

In this report, we show how in about one hour, AlphaClaim was able to find a high-quality invalidity ground for claim 1 of the '713 patent application.

#### Patent Application (US20240061713A1, Application 18/500,070)

Filed by Microsoft/Fungible on 11/01/2023. The patent application describes a multi-core DPU (Data Processing Unit) chip for stream processing, including network interfaces and methods to queue up and process packets. The application was published on 02/22/2024. As of May 18, 2024, there has been no office action associated with this application.

#### How AlphaClaim was used

We used AlphaClaim to automatically, accurately, exhaustively claim chart 923 prior art references. First, we provided AlphaClaim a claim construction, in technical language. This took about 15 minutes. The main AlphaClaim process, claim charting prior art, then took a little under one hour. AlphaClaim charted all the references we provided it, after it removed grace-period prior art. We used AlphaClaim analytics to break up the claim elements and find a combination of references that rendered the claim obvious.

#### The ground identified

AlphaClaim chose US7,567,567B2 as its base reference with a priority date of 04/05/2005 and a publication date of 07/28/2009. For the first element of the claim ("an integrated circuit comprising"), AlphaClaim relied on the "Cavium Networks OCTEON Plus CN50XX Hardware Reference Manual" v0.99E of July 2008, document file name "CN50XX-HRM-V0.99E", as <u>indexed by Google</u> in 2008.

#### **IDS Tagging**

AlphaClaim checks whether the chosen reference, or its family members, are mentioned in the IDS of the target patent or in the IDSes of the family members of the target patent. If any such mention is found, an AlphaIDS tag is generated indicating the type of mention and which specific patent/family are affected. Any references cited by the examiner during prosecution are automatically rejected.

In this instance, no such mention was found for the references cited.

Contact: ravi@alphaclaim.ai

Case Study by PriceWire, Inc.

Page 6 of 10

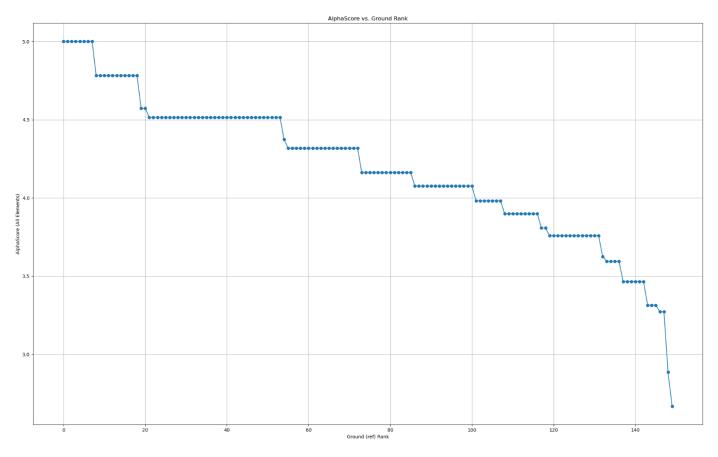

To provide more insight into how AlphaClaim works, we show a score graph for the top 150 references AlphaClaim charted. We then provide the unedited claim chart, AlphaScores, and explanations generated by AlphaClaim for its two-reference ground.

#### **Reviewed Grounds Scores**

AlphaClaim works by automatically, accurately, and exhaustively claim charting the prior art provided by the user to find the best invalidity ground possible. The chart shows the results of individual per-reference AlphaScores for the grounds reviewed in this particular case. While AlphaClaim reviewed 923 references for this case, we terminate the chart at 150 documents for viewability, as scores drop too low below that. The per-reference AlphaScore is computed as a mean of the per-element AlphaScores within each reference.

Contact: ravi@alphaclaim.ai

Case Study by PriceWire, Inc.

#### **AlphaClaim: Generated Claim Chart**

#### The two chosen references describe similar systems implemented a few years apart, thus enhacing motivation to combine:

| Feature                                                                     | US 7,567,567 B2 Base Reference (2005)                                                                                                                                            | Cavium Networks OCTEON Plus CN50XX Hardware<br>Reference Manual" v0.99E (2008)                                     |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| at least one interface configured to<br>send and receive stream data units, | In the integrated network interface unit 1300, portions of the four<br>port network interface unit 1200 are included within an<br>integrated solution in which network functions | Packets and control information can flow to/from CN50XX via<br>any of the RGMII, GMII, MII, or PCI interfaces.     |

| a plurality of programmable processing cores, and                           | The functional associations of the processing entities 120 a-n are                                                                                                               | High-performance architecture with up to two cnMIPS™<br>processor cores CN5020 has two processor cores             |

| a plurality of work unit queues                                             | The network interface unit 110 enables a relatively unconstrained<br>number of queues between a network interface and the<br>processing entities 12                              | POW implements eight input work queues. The different work queues can be used to provide different service levels. |

### This is the unedited output from AlphaClaim. Any legal document (e.g., Office Action or IPR petition) would be drafted by a professional based on this output.

#### Note: the "claim construction" referenced by AlphaClaim is user-provided. This took about 15 minutes to create.

| Claim Element<br>(US20240061713A1<br>claim 1) | Reference: AlphaClaim's Extracted Excerpt                                                                                       | Alpha-<br>Score | AlphaClaim's Explanation                                                                                                                     |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| A device comprising:<br>an integrated circuit | Cavium Networks OCTEON Plus CN50XX Hardware Reference<br>Manual (2008): CN50XX includes many core instructions beyond the       | 5.0             | <ol> <li>**Integrated Circuit Type**: The Excerpt describes CN50XX,<br/>which appears to be a network processor or communications</li> </ol> |

| comprising:                                   | standard MIPS64 integer (version 2) instructions. These include                                                                 |                 | processor, given its functionalities related to packet processing,                                                                           |

|                                               | instructions to accelerate packet processing, security processing, and                                                          |                 | security processing, and memory/cache processing.                                                                                            |

|                                               | memory/cache processing. There is extensive hardware acceleration on                                                            |                 | 2. <b>**</b> Packet Processing <b>**</b> : The Excerpt mentions instructions to                                                              |

|                                               | CN50XX, but the CPU cores direct the complicated higher-layer                                                                   |                 | accelerate packet processing and in-line hardware for packet                                                                                 |

|                                               | application-specific processing.                                                                                                |                 | processing.                                                                                                                                  |

|                                               |                                                                                                                                 |                 | 3. <b>**</b> Security Processing <b>**</b> : The Excerpt includes instructions for                                                           |

|                                               | 1.1.4 Flexible Packet/Control Interfacing                                                                                       |                 | security processing.                                                                                                                         |

|                                               | Packets and control information can flow to/from CN50XX via any of the RGMII, GMII, MII, or PCI interfaces. The RGMII interface |                 | <ol> <li>**Hardware Acceleration**: The Excerpt details extensive<br/>hardware acceleration for various tasks.</li> </ol>                    |

|                                               | supports up to three ports, and the PCI interface supports one port. This                                                       |                 | 5. **Core Partitioning**: The Excerpt describes core partitioning                                                                            |

|                                               | means that internally, CN50XX can support up to a total of four ports.                                                          |                 | for different functions.                                                                                                                     |

|                                               | CN50XX hardware efficiently transfers packets via the PCI interface.                                                            |                 | 6. **Packet/Control Interfacing**: The Excerpt mentions packet                                                                               |

|                                               | There is one input and one output port. CN50XX supports all PCI                                                                 |                 | and control interfacing via RGMII, GMII, MII, or PCI interfaces.                                                                             |

|                                               | transfer modes and also includes multiple DMA engines, whose                                                                    |                 | 7. **Work Queuing, Scheduling, Ordering, and Synchronization**:                                                                              |

|                                               | features can be used to support per-flow queueing in the PCI host                                                               |                 | The Excerpt explains work queuing, scheduling, ordering, and                                                                                 |

|                                               | memory.                                                                                                                         |                 | synchronization mechanisms, including tag values for                                                                                         |

|                                               |                                                                                                                                 |                 | ordering/synchronization.                                                                                                                    |

# AlphaClaim

| Claim Element<br>(US20240061713A1<br>claim 1)                                     | Reference: AlphaClaim's Extracted Excerpt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Alpha-<br>Score | AlphaClaim's Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                   | <br>In-line Packet-Processing Hardware Acceleration<br>The CN50XX has in-line hardware to offload from the cores all data<br>movement, many common packet-parsing functions, and other<br>important calculations. The in-line hardware completely offloads the<br>work from the cores. The CN50XX in-line packet-processing hardware<br>units complete the following tasks before a core receives a packet:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | The Excerpt matches the claim construction very closely. It<br>describes an integrated circuit (CN50XX) that fits the categories of<br>a network processor or communications processor. It covers all<br>required functionalities, including packet processing, security<br>processing, acceleration, core partitioning, packet/control<br>interfacing, packet-processing hardware acceleration, and work<br>queuing, scheduling, ordering, and synchronization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                   | Hardware Work Queuing, Scheduling, Ordering, and Synchronization<br>CN50XX hardware maintains a work queue in an on-chip hardware<br>unit. This structure provides a primary on-chip communication<br>mechanism between the cores and the hardware units on CN50XX.<br>Both hardware and core software can contribute work to the work<br>queue. The core software can request work at any time, which it<br>becomes aware of either through polling or by interrupts. The hardware<br>schedules the work for the cores. For example, the in-line input packet<br>processing hardware presents an input packet to the CPU cores by<br>creating and submitting a work queue entry to the queue. The core<br>software receives the packet by obtaining the associated work.<br>CN50XX has many ordering/synchronizations mechanisms available to<br>core software, but one important one is closely integrated with the<br>work queueing/scheduling hardware. This hardware<br>orders/synchronizes based on tag values associated with the<br>packet/work. |                 | Note: For this element, we instructed AlphaClaim to look for a network, communications or data processor integrated circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| at least one interface<br>configured to send<br>and receive stream<br>data units, | <b>Base Reference (2005):</b> Referring to FIG. 13, a schematic block diagram of an example of an integrated network interface unit 1300 is shown. In the integrated network interface unit 1300, portions of the four port network interface unit 1200 are included within an integrated solution in which network functions are included with a processor core. (The processor core is omitted from the Figure for clarity purposes). More specifically, the integrated network interface unit 1300 includes a transmit DMA module 812, a transmit FIFO reorder logic module 814, a receive FIFO module 816, a receive packet classifier module 818, and a receive DMA module 820. The integrated network interface unit 1200 also includes a media access control (MAC) module 830 and a system interface module 832                                                                                                                                                                                                                                  | 5.0             | The excerpt explicitly states the presence of an "integrated network<br>interface unit 1300" which, according to the useful terminology, is<br>an integrated solution that includes portions of a network interface<br>unit with network functions integrated with a processor core. This<br>directly matches the claim construction requirement that the device<br>or processor must have at least one network interface. The excerpt<br>further details the components of the integrated network interface<br>unit, reinforcing the presence of network interface capabilities<br>within the described device.<br>The claim construction is met by the excerpt's description<br>of the integrated network interface capabilities as part of an<br>integrated solution with a processor core. There is no deviation<br>from the claim construction in the excerpt; it directly states the<br>presence of a network interface within the device, fulfilling the<br>strong requirement set by the claim construction. |

# AlphaClaim

| Claim Element<br>(US20240061713A1<br>claim 1)                                                                                                                                                                                                                                                                                    | Reference: AlphaClaim's Extracted Excerpt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Alpha-<br>Score | AlphaClaim's Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a plurality of<br>programmable<br>processing cores, and                                                                                                                                                                                                                                                                          | <b>Base Reference (2005):</b> The functional associations of the processing<br>entities 120 a-n are illustrated by the dashed boundaries designated by<br>reference numerals 310 a-d. The functional association of processing<br>entity 120 a and memory system 130 designated by reference numeral<br>310 a is a "hypervisor" that is responsible for managing the partitioning<br>and association of the other processing entities, as will be described in<br>greater detail hereinbelow In the asymmetrical processing system<br>illustrated in FIG. 3, the specific assignment and mapping of well<br>defined subfunctions or sessions to preassigned processing entities is<br>done to increase efficiency and throughput. Any number of processing<br>entities can be assigned to a processing task that does not directly<br>involve a network interface resource, such as the N processing entities<br>120c-e. Likewise, any number of processing entities can be assigned to<br>perform a network functionality, protocol or hardware function, such as<br>the M processing entities 120 f-n illustrated in FIG. 3. The present<br>invention uses computer resources for network specific functions that<br>could be low level or high level.                                | 5.0             | The Excerpt explicitly mentions the presence of multiple processing<br>entities (120 a-n), which aligns with the requirement from the claim<br>construction for the device to have multiple processors or<br>processing cores. The description of these processing entities being<br>assigned to different tasks, with some handling network<br>functionalities and others handling non-network tasks, further<br>supports the notion of a multi-processor or multi-core system. The<br>mention of a hypervisor managing the partitioning and association<br>of these processing entities implies a complex system designed to<br>utilize multiple processing units efficiently. The Excerpt does not<br>merely imply but explicitly states the involvement of multiple<br>processing entities, which satisfies the claim construction's<br>requirement for the Excerpt to state that the device has multiple<br>processors or processing cores.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| a plurality of work<br>unit queues, wherein<br>each work unit queue<br>of the plurality of<br>work unit queues is<br>associated with one<br>of the programmable<br>processing cores and<br>configured to store a<br>plurality of work<br>units enqueued for<br>processing on the one<br>of the programmable<br>processing cores, | <b>Base Reference (2005):</b> The network interface unit 110 enables a relatively unconstrained number of queues between a network interface and the processing entities 120. The number of queues is related to the number of processing entities 120. The network interface unit 110 coordinates the servicing of resources such as shared queues. The network interface unit 110 provides for affinity between stateful sessions and processors over time. The network interface unit 110 coordinates interrupt driven packet arrival notification. The network interface unit 110 lowers DMA latency and increases DMA bandwidth to correspond to memory accesses. The network interface unit 110 takes into account multiple packet memory representations. The network interface unit 110 coordinates asynchronous interrupt notifications to minimize processing penalties associated with taking an interrupt. The network system 100 provides multiple queues between a network interface and a plurality of processing entities 120. The multiple queues correspond to the number of processing entities 120. Additionally The network system 100 preserves relevant packet ordering and servicing of multiple queues from multiple processors without coordination overhead. | 5.0             | <ol> <li>**One queue per processing core**: The Excerpt explicitly states<br/>that the number of queues corresponds to the number of processing<br/>entities (120). Given the definition of processing entities as entities<br/>that can quickly determine the reason they were activated, this<br/>aligns with the claim construction's requirement of having one<br/>queue per processing queues**: While the Excerpt does not use<br/>the phrase "packet processing queues" verbatim, it discusses the<br/>coordination of interrupt driven packet arrival notification, lowering<br/>DMA latency, and increasing DMA bandwidth, which are all<br/>relevant to packet processing. The context of coordinating servicing<br/>of resources such as shared queues and preserving relevant packet<br/>ordering further implies that the queues are indeed used for packet<br/>processing.</li> <li>**Matching Claim Construction**: The Excerpt matches the<br/>claim construction by describing a system where the number of<br/>queues is directly related to the number of processing cores<br/>(entities), and these queues are used in the context of network<br/>packet processing. The detailed functionalities described, such as<br/>coordination of interrupt notifications, lowering DMA latency, and<br/>preserving packet ordering, are all functionalities that support the<br/>efficient processing of packets in a system with one queue per<br/>processing core.</li> </ol> |

| Claim Element<br>(US20240061713A1<br>claim 1)                                                                                                                                                                                                                              | Reference: AlphaClaim's Extracted Excerpt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Alpha-<br>Score | AlphaClaim's Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wherein each work<br>unit of the plurality<br>of work units is<br>associated with one<br>or more of the stream<br>data units; and                                                                                                                                          | N/A, implied by other elements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N/A             | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| a queue manager<br>executable on a data<br>plane operating<br>system, wherein the<br>queue manager is<br>configured to<br>serialize packet<br>processing such that<br>data packets of a<br>same packet flow are<br>processed by a same<br>programmable<br>processing core. | <b>Base Reference (2005):</b> The hash table approach uses a mechanism for load balancing the IP packets to the appropriate processing entity 120 based on transmit affinity. If the operating system 430 wants to drive the affinity from a transmit perspective, then the operating system 430 exploits the hash table interface provided by the network interface unit 110. The application sourcing data running on a particular processing entity 120 (e.g., CPU#n) results in the network interface unit device driver 420 programming the hash table 950 so that received packets for that flow are sent to the Particular processing entity 120 (e.g., CPU#n). The hash table 950 provides the capabilities to manage a large number (e.g., four million) of flows. Each entry in the hash table 950 allows a flow to have a well-defined processing entity 120 plus some pointer, e.g., a pointer to the connection structure Before sending out a TCP SYN packet for active open or before sending TCP SYN ACK or TCP ACK, the entries in the hash table 950 are updated according to the processing entity 120 on which the connection is being initiated or terminated as the case may be. Updating the hash table allows subsequent packets for that flow to come to the same processing entity 120. | 5.0             | The Excerpt precisely matches the claim construction by describing<br>a method (the hash table approach) that maintains packet ordering<br>for packets belonging to the same flow. It ensures that packets of<br>the same flow are processed by the same processing core<br>(processing entity 120) by using a hash table to load balance IP<br>packets based on transmit affinity. The operating system (430) and<br>network interface unit device driver (420) work together to program<br>the hash table (950) to direct packets for a specific flow to a<br>particular processing entity. This is explicitly stated as being done<br>before sending out TCP SYN, TCP SYN ACK, or TCP ACK<br>packets, ensuring that subsequent packets for that flow come to the<br>same processing entity. The Excerpt directly addresses the claim<br>construction's requirements by detailing a method that maintains<br>flow consistency and processor affinity in packet processing. |